Versal Premium VP1902 är framförallt tänkt för asicutvecklare som behöver verifiera sina kretsar innan de går i produktion. Jätte-FPGA består av ett antal chiplets som tillsammans ger dubbelt så många sexvägs-logikceller som föregångaren och dessutom är störst på marknaden, enligt AMD Xilinx.

Versal Premium VP1902 är framförallt tänkt för asicutvecklare som behöver verifiera sina kretsar innan de går i produktion. Jätte-FPGA består av ett antal chiplets som tillsammans ger dubbelt så många sexvägs-logikceller som föregångaren och dessutom är störst på marknaden, enligt AMD Xilinx.

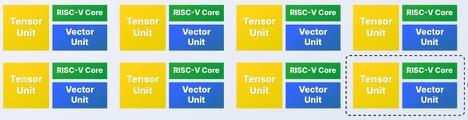

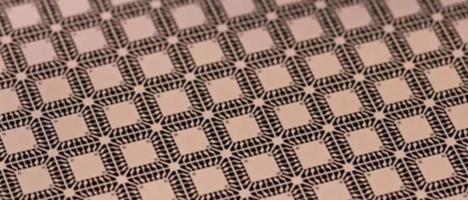

Föregångaren, Virtex UltraScale+ VU19P lanserades 2019 och tillverkas i en 16 nm-process medan Versal Premium VP1902 körs i en 7 nm-process. Bytet av process är en viktig förklaring till att antalet logikceller kunnat dubbleras till 18,5 miljoner. Vill man istället räkna antalet grindar blir det 60 miljarder. Att de är fördelade över fyra kiselbitar – chiplets – är däremot ingen nyhet, så har AMD Xilinx gjort i mer än tio år för de största FPGA:erna.

Marknaden för dessa extremt dyra kretsar är framförallt emulatorer och prototypsystem som används vid utveckling av nya asicar och systemkretsar. Och ju större FPGA:erna är, desto snabbare går verfieringen vilket hänger samman med att de rymmer större block av de kretsar de emulerar. AMD Xilinx har i egna tester kommit fram till att det kan handla om så mycket som fem gånger snabbare jämfört med den tidigare generationen.

Förutom storleken bidrar också den dubblerade IO-bandbredden till prestandalyftet. Det handlar om drygt 2300 generella in- och utgångar på 3,2 Gbit/s plus upp till 160 transceivrar – beroende på modell – som klar upp till 112 Gbit/s.

Vidare finns två ARM-kärnor i form av Cortex A72 plus två Cortex R5F, hårda IP-block för PCIe Gen5, Ethernet och DDR-minnen. Allt knyts ihop av Versals programmerbara nätverksprocessor, NoC.

Kretsen kommer kapslad i en HDIO och upptar 77,5x77,5 mm på kortet.

Utvalda kunder ska få sampel under tredje kvartalet och kommersiell produktion ska starta tidigt nästa år.